#### 3.4 CPU overview

#### 3.4.1 PCD1.M1xx

| Differentiation of          | PCD1.M110                                          | PCD1.M120                       | PCD1.M130               | PCD1.M125   | PCD1.M135               |  |  |  |

|-----------------------------|----------------------------------------------------|---------------------------------|-------------------------|-------------|-------------------------|--|--|--|

| base units (general)        |                                                    |                                 |                         |             |                         |  |  |  |

| Number of inputs/outputs or | 641)                                               |                                 |                         |             |                         |  |  |  |

| I/O module sockets          | 4                                                  |                                 |                         |             |                         |  |  |  |

| I/O modules                 | all PCD2 I/O modules except PCD2.Gxxx              |                                 |                         |             |                         |  |  |  |

| Processor                   | 68340 @ 16 MHz                                     |                                 |                         |             |                         |  |  |  |

| Processing time             |                                                    |                                 |                         |             |                         |  |  |  |

| Bit instruction             | z.B.                                               | ANH I                           | F 0 5 μs²               | )           |                         |  |  |  |

| Word instruction            | z.B.                                               | ADD I                           | R 0 20 µs               | $S^{2)}$    |                         |  |  |  |

|                             |                                                    | I                               | R 1                     |             |                         |  |  |  |

|                             |                                                    | I                               | R 2                     |             |                         |  |  |  |

| Firmware                    | 1 PROM in socket; from first soldered Flash Memory |                                 |                         |             |                         |  |  |  |

|                             | half of 2                                          | 004 soldered                    | modules <sup>7)</sup>   |             |                         |  |  |  |

| Minimum PG5 version         | 1.0, for TCP/IP 1.1                                |                                 |                         | 1.3.120     | 1.3.120                 |  |  |  |

| User memory                 |                                                    |                                 |                         |             |                         |  |  |  |

| RAM basic set up            |                                                    | 17 Kbytes3)                     | 128 KByte               |             |                         |  |  |  |

| Expansion with RAM,         | up to                                              | 128 Kbytes a                    | 128 512 KBytes          |             |                         |  |  |  |

| EPROM or                    |                                                    | 128 Kbytes added 128 128 KBytes |                         |             |                         |  |  |  |

| Flash EPROM                 | up to                                              | 112 Kbytes added 112 448 KBytes |                         |             |                         |  |  |  |

| Clock (RTC)                 | no <sup>4)</sup>                                   | yes, deviation < 25 ppm         |                         |             |                         |  |  |  |

| Data protection             | 30 days                                            | 7 days with                     | 1-3 years <sup>5)</sup> | 7 days with | 1-3 years <sup>5)</sup> |  |  |  |

|                             | with                                               | Super Cap                       | with CR                 | Super Cap   | with CR                 |  |  |  |

|                             | Super Cap                                          |                                 | 2032                    |             | 2032                    |  |  |  |

|                             |                                                    |                                 | lithium                 |             | lithium                 |  |  |  |

|                             |                                                    |                                 | battery                 |             | battery                 |  |  |  |

| Interrupt inputs            | no                                                 | 2                               |                         |             |                         |  |  |  |

| Maximum input frequency     | -                                                  | 1 kHz <sup>6)</sup>             |                         |             |                         |  |  |  |

- 1) Using digital I/O modules PCD2.E16x or A46x with 16 I/Os each

- 2) Typical values; the processing time is dependent on the load on the communication ports

- 3) When extended memory is used, 13 Kbytes of the base memory can be used to store RAM texts and DBs (text/DB addresses ≥ 4000)

- 4) When the HeaVAC library is used: The absence of the clock is reported as an error when processing the HeaVAC initialization block, and the clock timers cannot be used

- 5) The period given is a buffer time; it is dependent on the ambient temperature (a higher temperature means a shorter buffer time)

- 6) The 1kHz applies with a pulse/pause ratio of 1:1 and refers to the total frequencies of the two inputs

- 7) T(Updates of the firmware via PGU possible)

| Differentiation of base units (ports)                              | PCD1.M110                                                                     | PCD1.M120                                       | PCD1.M130                                   | PCD1.M125 | PCD1.M135                                              |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------|-----------|--------------------------------------------------------|--|--|

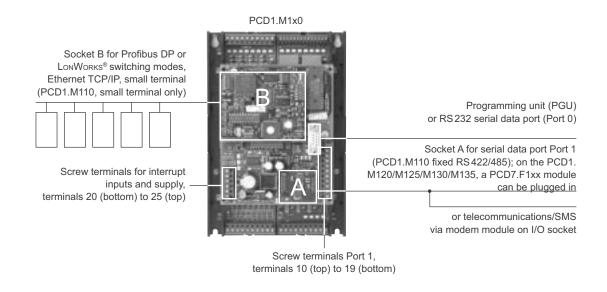

| Programming interface                                              | PGU port D-Sub socket, 9-pole <sup>1)</sup> (for PCD8.K111 programming cable) |                                                 |                                             |           |                                                        |  |  |

| Serial data port<br>Socket A                                       | 1<br>RS 422,<br>RS 485,<br>built-in                                           | S485, TTY current loop 20mA, plug-in (PCD7.F1xx |                                             |           |                                                        |  |  |

| Field bus connections                                              | -                                                                             |                                                 | Saia®S-Bus Ethernet- TCP/IP (Ether-S- Bus)² | -         | Ethernet-<br>TCP/IP<br>(Ether-S-<br>Bus) <sup>2)</sup> |  |  |

|                                                                    | -                                                                             | Profibus DP<br>LONWORKS                         |                                             |           |                                                        |  |  |

| Socket B for network and/or data port, LED display, small terminal | for PCD7.<br>D162<br>terminal kit<br>only <sup>3)</sup>                       | yes <sup>3)</sup>                               |                                             |           |                                                        |  |  |

- 1) Can also be used as a serial data port, e.g. to connect a terminal; but this hampers troubleshooting with the debugger

- 2) Ethernet TCP/IP available as a configured system: PCD1.M130F650. If installed later, the cover must be replaced (item-no. 4 104 7409 0)

- 3) We recommend ordering the PCD2.D16x terminal kit mounted on the controller. If installed later, the cover must be replaced (item-no. 4 104 7338 0)

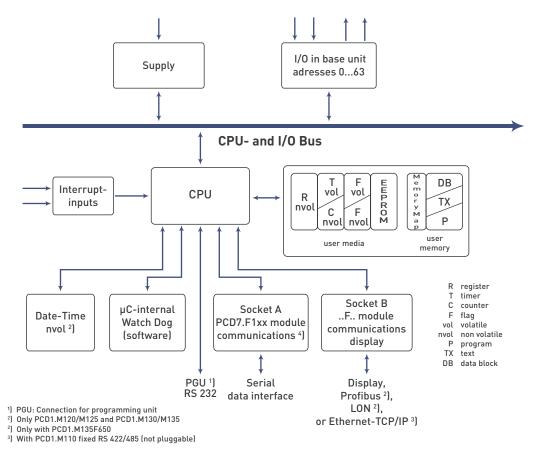

# 3.4.2 Block diagram: PCD1.M1xx

Removing the cover exposes components that are sensitive to electrostatic discharges.

**Recommendations:** Immediately before touching the electronic circuits, briefly touch the metal housing of the PGU connection. It is safer to use an anti-static wrist band, connected to the Minus of the system.

When the power is switched on, no operations (such as moving jumpers or (un)plugging I/O modules) should be attempted.

To prevent loss of data, batteries should be changed with the power switched on.

### 3.4.3 Hardware and firmware versions for the PCD1

The firmware versions for the PCD1.M1xx are generally upwardly compatible in terms of hardware, so old CPUs can be fitted with new firmware, in order to take advantage of new functions. This feature is highly valued, and we will try to retain it for as long as possible; however, we cannot guarantee this.

At this point, the following known restrictions apply:

The use of intelligent communication modules such as Profibus DP, LON and Ethernet requires the minimum hardware and firmware versions. Please refer to the manuals for the relevant communication modules

3

## 3.4.4 Firmware Upgrade for the PCD1.M110, PCD1.M120 and PCD1.M130

The firmware for the PCD1.M1x0 is stored in a PROM. These chips can only be programmed once. With blank chips (item-no. 4 502 7178 0) and an EPROM burner with adapter for PLCC44 chips (e.g. Galep-4 with adapter 210841), new firmware chips can be burnt at any time. The file with the latest firmware version can be downloaded from <a href="https://www.sbc-support.ch">www.sbc-support.ch</a>.

At this point, the following known restrictions apply:

In the course of 2004, soldered firmware chips were adopted; for a firmware update, these controls have to be returned to the factory

### 3.4.5 Firmware Upgrade for the PCD1.M125 and PCD1.M135

The Firmware is stored in a Flash EPROM, soldered to the motherboard. A firmware update can be applied by downloading a new version with the PG5. The procedure is as follows:

- Go to www.sbc-support.ch and download the latest firmware version.

- Establish a connection between PG5 and the CPU, as for a download of an application (depending on the facilities available, serially via PGU cable, modem<sup>1)</sup>, USB, Ethernet).

- · Open the Online Configurator and go offline.

- From the Tools menu, select "Update Firmware", then use the Browse function to select a path to the file for the new firmware version. Ensure that only one file is selected for downloading.

- Start the download.

- After the download, the power supply to the PCD must not be interrupted for 3

minutes (CPLD programming sequence). Otherwise, the CPU may be blocked in

such a way that it needs to be returned to the factory.

- 1) A modem connection is not always reliable. A modem may become blocked in such a way that remote access is no longer possible. In such cases, an on-site visit will be necessary. Other connection options are preferable.